| Posted: Dec 27, 2016 |

Scientists design new heat-guiding device that is thinner than a hair

(Nanowerk News) Researchers at Singapore University of Technology and Design (SUTD), University of Bath and University of Cambridge have designed for the first time a heat-guiding structure on the size of nanometers that can steer heat away from, or even towards critical regions of current silicon (or advanced chalcogenide) chips through computer simulations.

|

|

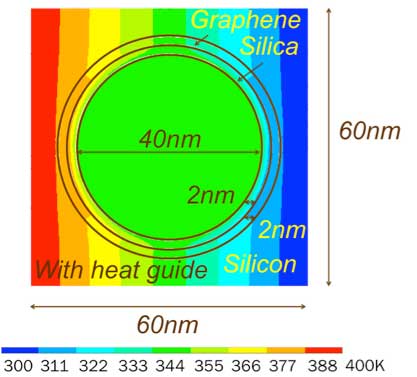

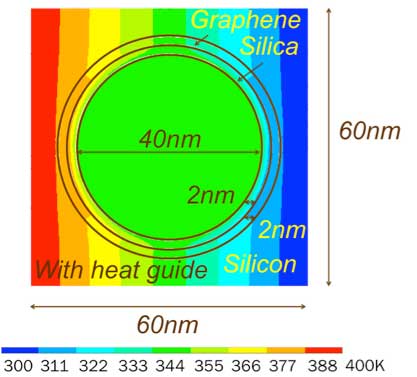

Heat guides were formed using graphene and silicon dioxide. Graphene has been previously demonstrated to be an excellent material that allows heat to flow easily along its layers, while silicon dioxide has been shown to be a good medium that resists heat. For example, by stacking these materials together, they can produce an effect of 'relative heat flow', making a selected region of silicon or chalcogenide 'invisible' to heat.

|

|

| This is an example of a heat guide in the form of rings which can 'hide' the central region of silicon from heat. (Image: Singapore University of Technology and Design)

|

|

Co-author, Assistant Professor Desmond Loke from SUTD, said, “Previous research has demonstrated heat-guiding devices showing these effects on the size of micrometers. However, we can now show that this works for structures that are 1,000 times smaller and on silicon or advanced phase-change alloys, making it more useful to remove or keep heat to manufacture tinier electronic devices for current applications, such as smartphones, internet of things (IoT), virtual reality (VR), data centers, etc.”

|

|

Using purely heat through such heat-guiding structures, the scientists showed that it was even possible to perform a complete set of Boolean logic operations, and an entire series of 'spike-timing-dependent plasticity' learning processes.

|

|

“These heat guides could find widespread uses in more compact integrated circuits for future applications, such as reconfigurable computing, deep learning, artificial intelligence (AI), etc,” Loke added.

|

|

This research is funded by a SUTD Temasek Seed grant and published in the journal ACS Applied Materials and Interfaces ("Design of a Nanoscale, CMOS-Integrable, Thermal-Guiding Structure for Boolean-Logic and Neuromorphic Computation").

|