| Posted: Jun 14, 2017 |

Laying the foundations for hybrid silicon lasers

(Nanowerk News) Producing semiconductor lasers on a silicon wafer is a long-held goal for the electronics industry, but their fabrication has proved challenging. Now, researchers at A*STAR have developed an innovative way to manufacture them that is cheap, simple and scalable (ACS Photonics, "Fabrication and Demonstration of III–V/Si Heterocore Microcavity Lasers via Ultrathin Interlayer Bonding and Dual Hard Mask Techniques").

|

|

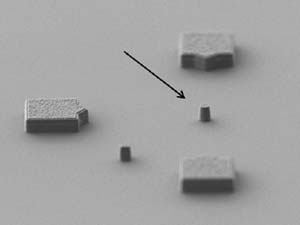

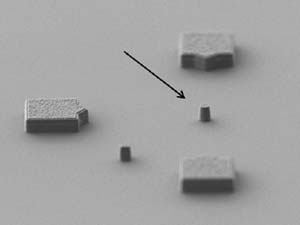

| Oblique angle scanning electron microscopy image of a 500 nanometer diameter microdisk. (Image: A*STAR Data Storage Institute)

|

|

Hybrid silicon lasers combine the light-emitting properties of group III–V semiconductors, like gallium arsenide and indium phosphide, with the maturity of silicon manufacturing techniques. These lasers are attracting considerable attention as they promise inexpensive, mass-producible optical devices that can integrate with photonic and microelectronic elements on a single silicon chip. They have potential in a wide range of applications, from short-distance data communication to high-speed, long-distance optical transmission.

|

|

In the current production process, however, lasers are fabricated on separate III–V semiconductor wafers before being individually aligned to each silicon device — a time-consuming, costly process that limits the number of lasers that can be placed on a chip.

|

|

To overcome these limitations, Doris Keh-Ting Ng and her colleagues from the A*STAR Data Storage Institute have developed an innovative method for producing a hybrid III–V semiconductor and silicon-on-insulator (SOI) optical microcavity. This greatly reduces the complexity of the fabrication process and results in a more compact device.

|

|

“It’s very challenging to etch the entire cavity,” says Ng. “Currently, there is no single etch recipe and mask that allows the whole microcavity to be etched, and so we decided to develop a new approach.”

|

|

By first attaching a thin film of III–V semiconductor to a silicon oxide (SiO2) wafer using a SOI interlayer thermal bonding process, they produced a strong bond that also removes the need for strong oxidizing agents, such as Piranha solution or hydrofluoric acid.

|

|

And by using a dual hard-mask technique to etch the microcavity that confined etching to the intended layer, they eliminated the requirement to use multiple overlay lithography and etching cycles — a challenging procedure.

|

|

“Our approach cuts down the number of fabrication steps, reduces the use of hazardous chemicals, and requires only one lithography step to complete the process,” explains Ng.

|

|

The work presents, for the first time, a new heterocore configuration and integrated fabrication process that combines low-temperature SiO2 interlayer bonding with dual hard-mask, single lithography patterning.

|

|

“The process not only makes it possible to produce heterocore devices, it also greatly reduces the challenges of fabricating them, and could serve as an alternative hybrid microcavity for use by the research community,” says Ng.

|