| Aug 22, 2011 |

Ultra-low-power readout architecture for MEMS/NEMS sensors

|

|

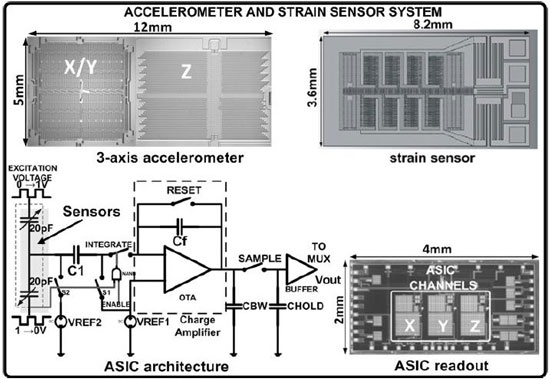

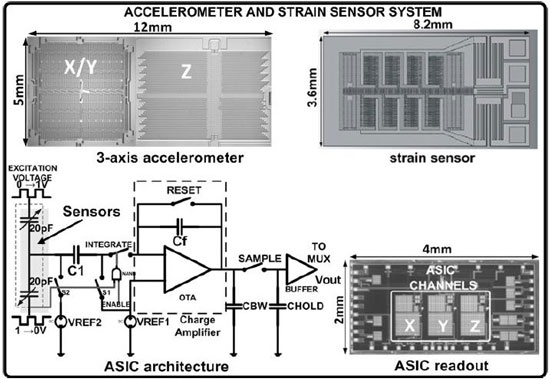

(Nanowerk News) Imec and Holst Centre report an ultralow-power readout ASIC for capacitive MEMS/NEMS-based sensors. The system can read both accelerometers and strain sensors in a half-bridge configuration. The gain is controlled by integrating pulses from the excitation voltage allowing accurate control of the SNR (signal-to-noise) ratio. We achieved a figure-of-merit of 4.41×10-20 F√(W/Hz) for a sensor range of ±2.0g and ±20,000µε over a 100Hz bandwidth. The system has also been designed to cancel residual motion artifacts.

|

|

| MEMS readout: Microphotographs of the accelerometer, strain sensor and readout ASIC and topology of a single channel capacitive readout.

|

|

With the growing number of MEMS sensors for all types of applications, there is a need for innovative, flexible and power-efficient readout architectures. These have to be able to read signals from a wide range of capacitive devices (such as accelerometers and strain sensors with different actuation voltages, sensitivities and resolutions). One particular interesting application field is the monitoring of building integrity, where the sensors have to measure displacements and stresses, as an indication for the integrity of structures during e.g. seismic events. Such applications impose resolution requirements of 1mg and 10µε for the accelerometer and strain sensor respectively, and a range of ±2.0g and ±20,000µε over a 100Hz bandwidth.

|

|

Most of the existing readout chips are custom-made for a particular sensor, which usually has a large sensitivity in a narrow band. Our architecture can interface with a variety of sensors without jeopardizing the power consumption. This is important for monitoring building integrity, which requires battery-operated systems to keep working for several years. It's also a cost-effective solution, since the same readout can be used for both accelerometers and strain sensors. Last, the system's flexibility is a major asset: sensors with different sensitivities, offsets and mismatch can easily be handled by modifying the timing and duty cycle of the excitation pulses.

|

|

Our readout architecture has the lowest reported equivalent acceleration noise level and the highest bandwidth. It offers a unique tradeoff between SNR, bandwidth, and power. The design was fabricated on TSMC 0.25µm CMOS with metal-insulator-metal capacitors. The total power consumption of the 3 channels is 15µW. The clock and excitation voltages for the sensors are external.

|